定制化硬件与系统交付案例

从单一通信模块的 IP 级定制,到满配业务接口的硬件板卡,再到含底层系统与上层网管的完整设备,以下是我们提供的典型交付形态。

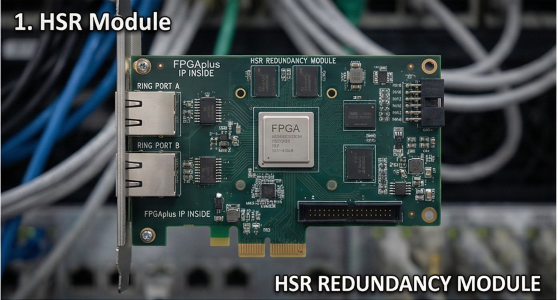

HSR_REDUNDANCY_BOARD

HSR_REDUNDANCY_BOARD

HSR 工业冗余环网逻辑定制

- 用户需求:为现有的成熟工业级交换机增加 IEC 62439-3 HSR 无缝冗余环网功能,实现真正的零丢包。

- 用户诉求:现有硬件基座极其成熟且备货量大,绝对无法推翻重来;但客户内部缺乏底层 FPGA 高速逻辑及协议开发的经验。

- 技术难点:在老旧硬件的严苛限制下,将 HSR 核心逻辑(帧复制、环网丢弃、序列号标签插入)与现有 MAC 层无缝对接,且跨时钟域处理要求极高。

- 替代优势:采用非侵入式 IP 嵌入。代为完成全部高速管脚约束与时序收敛,直接交付即插即用的 `.bit` 烧写文件,无需更改任何物理层设计。

- 成本优势:百万级存量硬件资产完美利旧。免去了重新打板、测试及重新过 EMC 认证的高昂试错成本,将上市时间缩短了 70%。

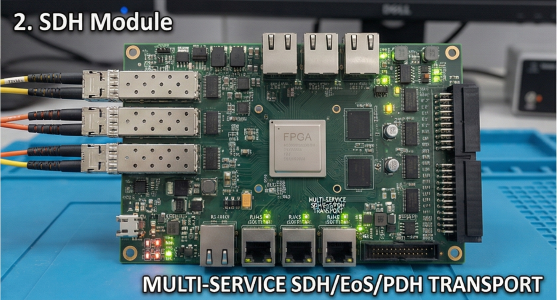

SDH_MULTISERVICE_PCBA

SDH_MULTISERVICE_PCBA

4光 + 4以太网 + 16E1 综合 SDH 业务模块

- 用户需求:面向传统 MSTP 现网改造,开发一款高集成度的多业务接入硬件板卡,同时兼容 PDH 与现代分组业务。

- 用户诉求:急需解决以往多芯片拼凑导致的功耗极高、PCB 面积过大以及信号串扰严重等老大难问题。

- 技术难点:需同时处理 16 路 E1 的 VC-12 复杂交叉、以太网 GFP/VCAT 虚级联映射,还要保障 4 路 STM-N 高速光口同时运行时的信号完整性 (SI) 与热耗散。

- 替代优势:重构为单片 FPGA 统筹核心逻辑。我们交付了经过 SI 仿真与严格阻抗控制的完整 PCBA,彻底打通高速布线瓶颈。

- 成本优势:精简的单芯片架构让 BOM 成本直接降低 40%;大幅降低了后期的硬件返修率,彻底释放了客户内部硬件团队的研发带宽。

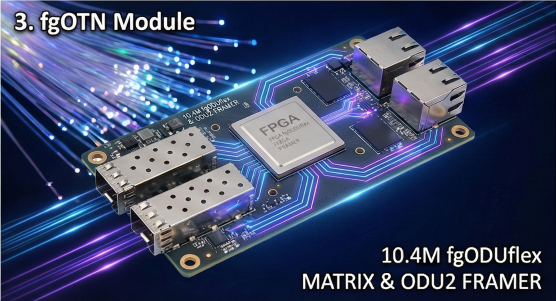

FGOTN_MATRIX_MODULE

FGOTN_MATRIX_MODULE

2光 + 2以太网 + 2口STM-1/4 集成 fgOTN 硬件模块

- 用户需求:面向算力网络与高品质专线,研发一款微型化的 fgOTN 接入核心组件。

- 用户诉求:必须满足信创要求(全国产化),同时要求核心网元具备极低的传输时延和高度灵活的无级带宽调度能力。

- 技术难点:需攻克极其复杂的、以 10.4M 为颗粒度的大规模 fgODUflex 交叉矩阵;并将 ODU2 高速成帧算法与各业务流的 GMP 异步映射机制在单片 FPGA 内融合。

- 替代优势:摒弃了国外商用成帧芯片的“黑盒”束缚,底层协议完全自主可控。架构具备极高的平台伸缩性,可平滑移植至纯国产 FPGA 平台。

- 成本优势:打破了国外高端商用通信芯片的垄断溢价,核心模块采购成本呈现断崖式下降,赋予了客户在投标报价时极大的让利空间。

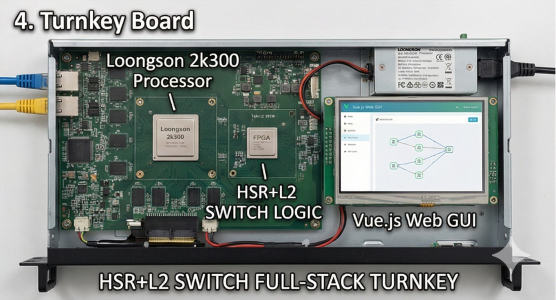

FULL_STACK_TURNKEY

FULL_STACK_TURNKEY

完整的 HSR + L2交换机 软硬一体板卡

- 用户需求:交付一款同时具备多端口二层汇聚与 HSR 环网保护能力的整机级核心板,并配备完整的设备网管后台。

- 用户诉求:客户团队专攻上层应用逻辑,极度缺乏国产化 CPU 硬件架构适配、嵌入式 OS 底层调优以及现代网管全栈的研发能力。

- 技术难点:基于龙芯 (Loongson) 2k300 的硬件主控设计;需在受限资源下解决高频日志写入导致 eMMC 磨损的难题(通过创新性引入 OverlayFS 与 initramfs 绑定解决);同时需打通底层 Net-SNMP AgentX 到前端 Vue.js 的数据链路。

- 替代优势:提供真正的 L4 级“交钥匙”工程。将复杂的跨时钟域逻辑、多线程 C/C++ 并发锁 (Mutex) 全部封装在底层。客户仅需通过 API 即可与 Vue.js GUI 交互。

- 成本优势:省去了组建包含 FPGA、硬件、驱动与前端开发全栈团队的数百万元人工开销。将跨界研发的死锁风险降至零。